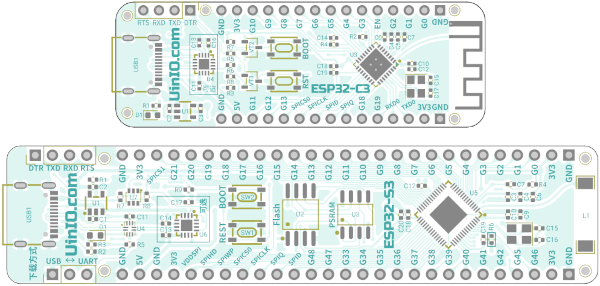

UINIO-MCU-ESP32 系列核心板电路设计

UINIO-MCU-ESP32C3

和 UINIO-MCU-ESP32S3

两款开源核心板,分别采用了上海乐鑫科技

推出的 ESP32-C3 以及 ESP32-S3

微控制器,两者均支持 2.4GHz Wi-Fi 与 Bluetooth

5.0

无线网络连接。本文旨在介绍两块核心板各个功能单元的硬件电路设计原理,其中

ESP32-C3 微控制器基于开源的 RISC-V

内核架构,拥有 22 个 GPIO 接口,主频高达

160MHz,板载 384KB 容量的 ROM,以及

400KB 容量的 SRAM 和 8KB 容量的 RTC

SRAM,支持的数字外设接口有

3 × SPI、2 × UART、1 × I²C、1 × I²S,而模拟外设接口则采用了

6 通道的 2 × 12 位 SAR 模/数转换器。

稍晚一些推出的 ESP32-S3 微控制器则是基于

Cadence 公司的 Xtensa Dual-Core 32-bit

LX7 架构,拥有 45 个 GPIO 接口,主频高达

240MHz,板载有 384KB 容量的 ROM,以及

512KB 容量的 SRAM 和 16KB 容量的 RTC

SRAM,支持的数字外设接口有

4 × SPI、3 × UART、2 × I²C、2 × I²S。而模拟外设接口采用了

20 通道的 2 × 12 位 SAR

模/数转换器。核心板的 KiCad 原理图以及 PCB

源文件,可以在我的 GitHub

仓库当中进行获取。

UINIO-MCU-ESP32C3 硬件设计

上海乐鑫科技

推出的 ESP32-C3 微控制器基于 RISC-V

架构,拥有 22 个 GPIO 接口,主频高达

160MHz,板载有 384KB 容量的 ROM,以及

400KB 容量的 SRAM 和 8KB 容量的 RTC

SRAM,支持的数字外设接口有

3 × SPI、2 × UART、1 × I²C、1 × I²S,而模拟外设接口方面则支持多达

6 通道的 2 × 12 位 SAR 模/数转换器。

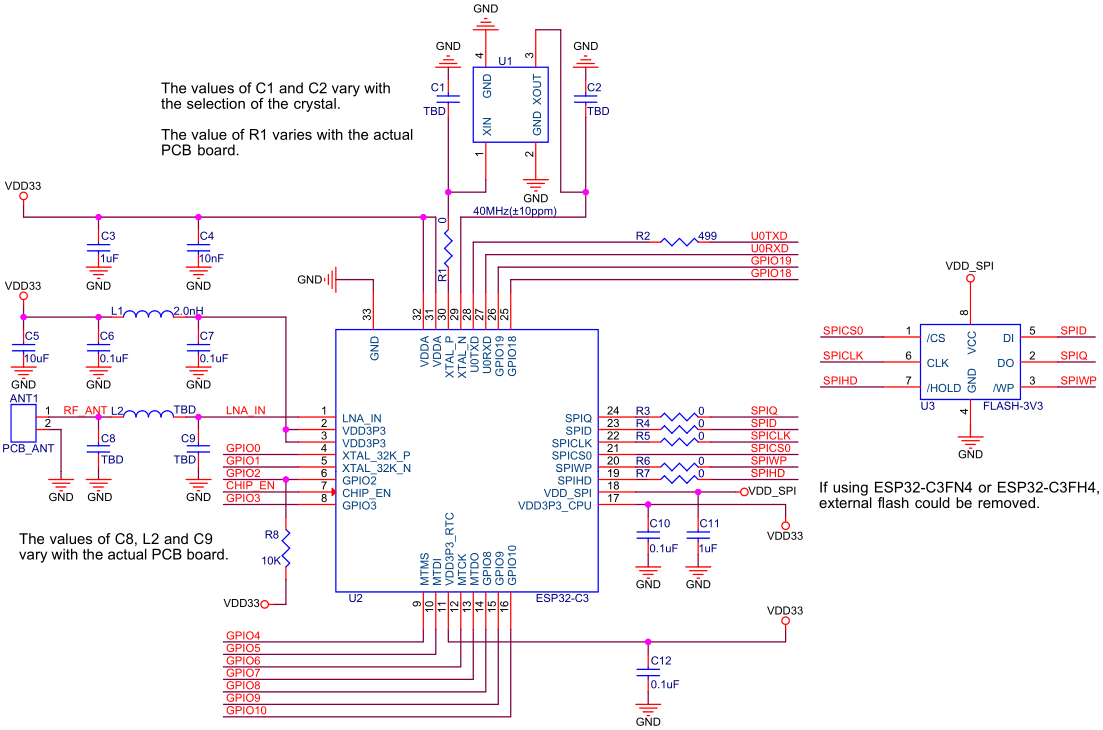

ESP32-C3 的外围电路设计较为简单,仅仅只需要

20 个左右的贴片电阻、电容、电感,以及

1 个无源晶振、1 个 SPI 接口的 Flash

存储芯片。其核心电路主要包括

电源、上电时序与复位、Flash 存储器、时钟源、射频天线、UART 串行通信、ADC 模/数转换、Strapping 引脚、GPIO 引脚、UART0 自动下载电路

等部分,下面展示了 ESP32-C3 官方给出的参考原理图:

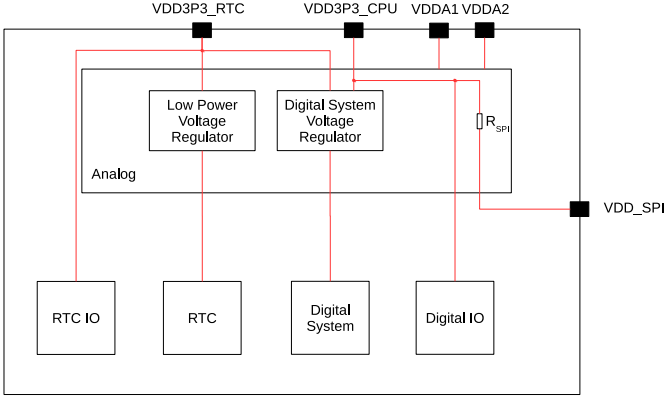

电源管理

ESP32-C3 一共拥有 VDDA1 和

VDDA2(模拟电源)、VDD3P3_RTC(RTC

电源)、VDD3P3_CPU(MCU 电源)

四组电源输入引脚,以及一组 VDD_SPI

引脚(电源输入/输出管脚,由 VDD3P3_CPU

通过电阻 \(R_{SPI}\)

进行供电,因而会相对于 VDD3P3_CPU

存在着一定的电压降)。

注意:当

VDD_SPI无需为外部进行供电时,也可以将其复用为GPIO11来进行使用。

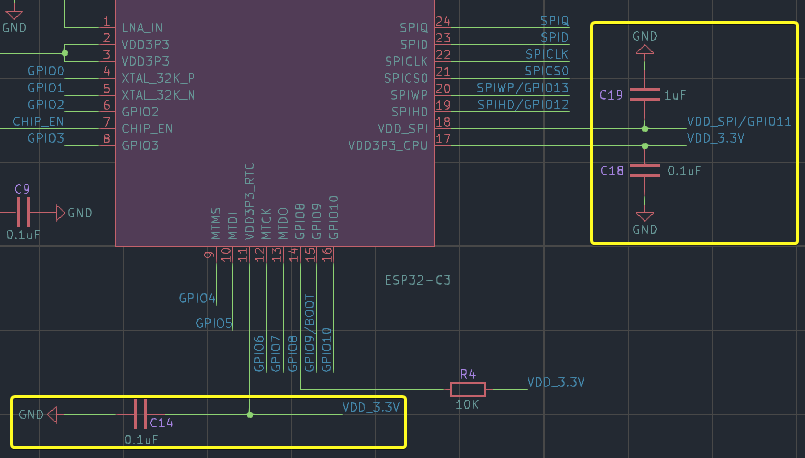

数字电源

ESP32-C3 的典型工作电压为

3.3V,而工作电流则需要达到

500mA 及以上。在 UINIO-MCU-ESP32C3

原理图当中,ESP32-C3 的第 11 和

17 引脚分别为 RTC 电源引脚和 MCU

电源引脚,工作电压介于 3.0V ~ 3.6V

范围之间,并且分别添加了 0.1µF 以及 1µF

的对地滤波电容。

注意:当使用

VDD_SPI作为外部 Flash 存储器的电源时,需要满足该款 Flash 存储芯片的最低工作电压要求,通常应当保证其电压值处于3.0V及以上的值。

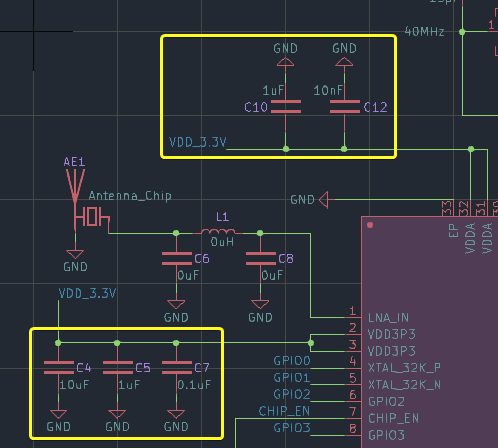

模拟电源

ESP32-C3 芯片的第

2、3、31、32

为模拟电源引脚,工作电压同样介于 3.0V ~ 3.6V 范围。

注意:当 ESP32-C3 工作在

TX状态下时,由于瞬时电流较大,可能会导致电源轨道塌陷(当电源与地之间的电流发生变化时,电源路径与接地路径之间的阻抗会产生一个压降,从而导致提供给芯片的工作电压被降低),所以官方建议在电源走线上增加了一个10µF电容,并且将其与0.1µF、1µF电容并联起来搭配使用。

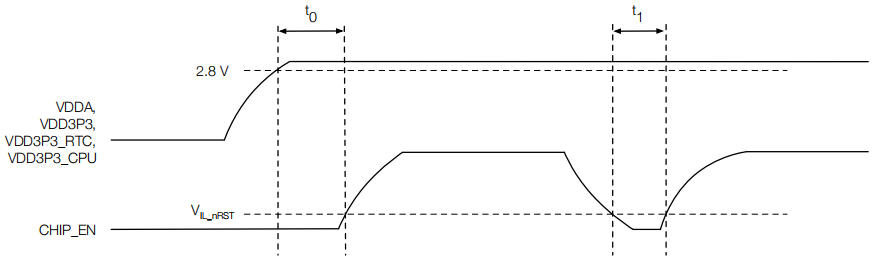

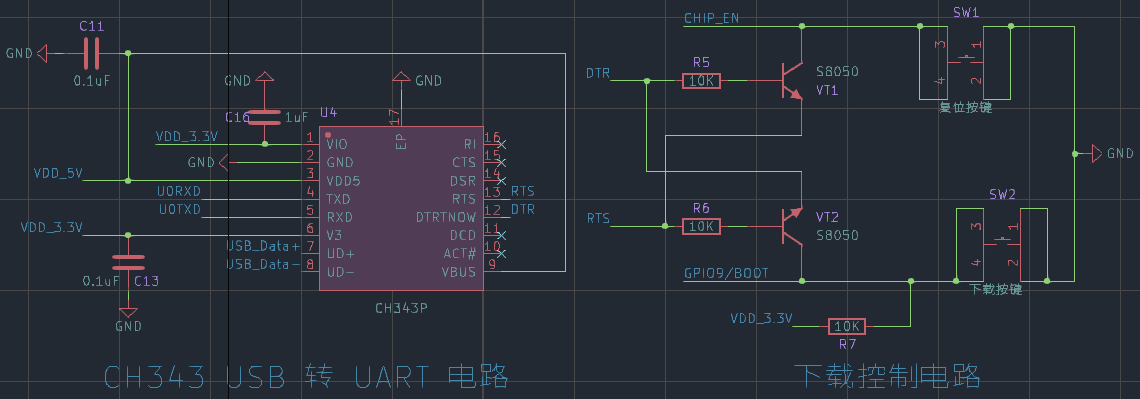

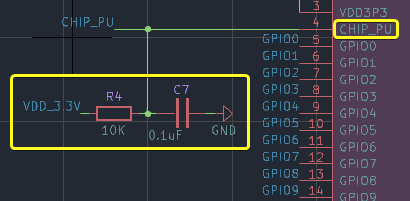

上电时序 & 复位

上电时序

ESP32-C3 的上电时序需要遵循:编号为 7

的使能引脚

CHIP_EN,上电时间必须晚于系统电源

3.3V 的上电时间。

| 参数 | 说明 | 最小值(微秒) |

|---|---|---|

| \(t_0\) | CHIP_EN 管脚上电时间晚于

VDDA、VDD3P3、VDD3P3_RTC、VDD3P3_CPU; |

50微秒 |

| \(t_1\) | CHIP_EN 引脚的电平低于 \(V_{IL\_{nRST}}\) 的时间; |

50微秒 |

注意:为了确保 ESP32-C3 在上电时电源的正常供电,

CHIP_EN引脚需要添加 RC 延时电路(典型取值为R = 10 kΩ,C = 1 µF,具体数值需要根据电源的上电时序和芯片的上电复位时序进行调整)。

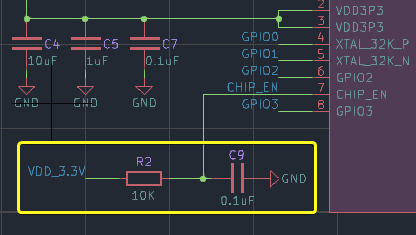

复位

ESP32-C3 可以通过 CHIP_EN

引脚进行复位,当 CHIP_EN

为低电平的时候,建议复位电平 \(V_{IL\_{nRST}}\) 的取值范围为 \((–0.3 \sim 0.25) \times VDD\)

伏。除此之外,为了防止外界干扰导致系统重启,建议尽量缩短

CHIP_EN 的 PCB 走线,并且添加上拉电阻

\(R_2\)

以及对地去耦电容 \(C_9\)。

注意:ESP32-C3 的

CHIP_EN引脚不可以处于浮空状态。

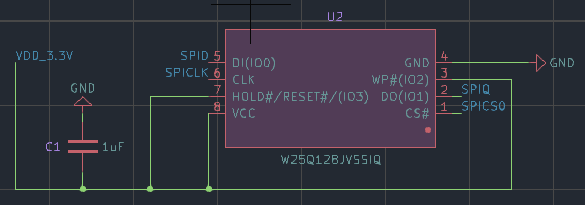

Flash 存储器

ESP32-C3 最大支持 16MB 容量的 Flash

存储器,可以选择使用 VDD_SPI 引脚输出的电源进行供电。在

UINIO-MCU-ESP32C3 当中,直接选择将 LDO

线性稳压器输出的 VDD_3.3V 作为 Flash

存储芯片的工作电源。

注意:如果采用了

VDD_SPI作为电源,那么建议在 SPI 总线引脚上预留一个0Ω串联电阻的封装位置,用于降低驱动电流、减小串扰、调节时序等后续调试工作。

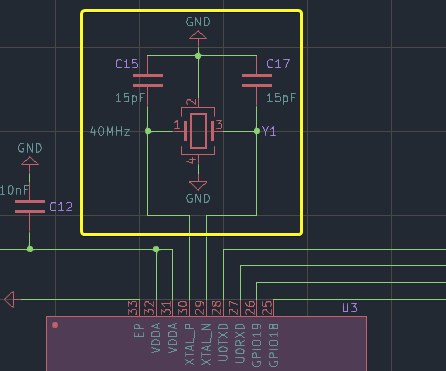

时钟源

ESP32-C3 可以使用外部晶振和外部 RTC两个时钟源。

外部晶振时钟源

ESP32-C3 只支持 40MHz 晶振(精度为

\(\pm 10 ppm\)),匹配电容

C15 和 C17

的取值需要经过测试之后再行确定。

外部 RTC 时钟源

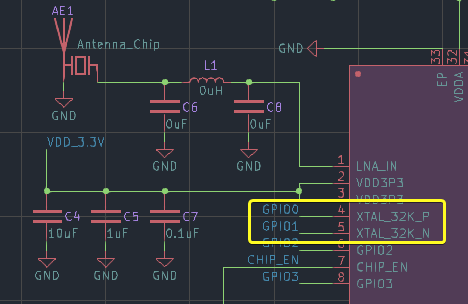

ESP32-C3 支持将 XTAL_32K_P 和

XTAL_32K_N 引脚,连接至外部的 32.768 kHz

晶振作为 RTC 实时时钟。而

UINIO-MCU-ESP32C3 为了获得更多的 GPIO 资源,索性直接将

XTAL_32K_P 和 XTAL_32K_N 引脚复用为

GPIO0 和 GPIO1 进行使用。

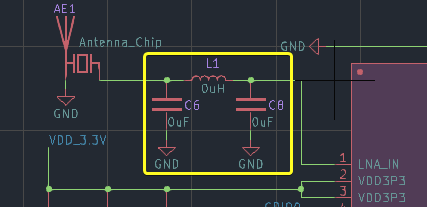

射频天线

UINIO-MCU-ESP32C3 在引出射频天线时,预留了 CLC 结构的 \(\pi\) 型阻抗匹配网络(具体参数需要根据实际天线的 PCB 布局来测定),以期获得最佳的发射功率:

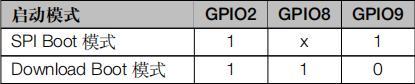

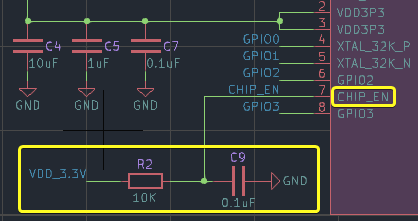

Strapping 引脚

ESP32-C3

在复位过程当中(上电复位、RTC 看门狗复位、欠压复位、模拟超级看门狗复位、晶振时钟毛刺检测复位),Strapping

引脚会将引脚上的电平状态采样并且存储到锁存器当中(锁存值为

0 或 1

),并且会一直保持到芯片掉电或者关闭。ESP32-C3

一共拥有 GPIO2、GPIO8、GPIO9 三个

Strapping 引脚(可以通过读取

GPIO_STRAP_REG 寄存器上的 GPIO_STRAPPING

字段,获得这三个引脚上面的状态值)。

使用外接上下拉电阻或者直接经由

GPIO,可以直接控制复位时 Strapping

引脚的电平状态。在复位完成之后,Strapping 引脚会转变为普通引脚。其中

GPIO9

默认连接内部的上拉电阻,如果该引脚悬空或者连接到外部的高阻抗电路,则锁存值默认为

1。ESP32-C3 的 Strapping

引脚启动模式配置,可以参考下面的表格:

| 引脚 | 默认 | SPI 启动模式 | 下载启动模式 |

|---|---|---|---|

| GPIO2 | 无 | 1 |

1 |

| GPIO8 | 无 | 无关 | 1 |

| GPIO9 | 内部上拉 | 1 |

0 |

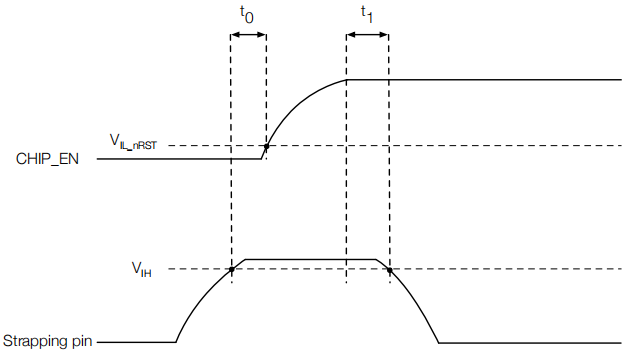

下图展示了 CHIP_EN 在上电前后,Strapping

引脚的建立时间 \(t_0\)(最少保持 0

毫秒)和保持时间 \(t_1\)(最少保持 3

毫秒)之间的关系:

GPIO 引脚

ESP32-C3 一共拥有 22 个 GPIO

引脚,通过配置对应的寄存器,可以为这些引脚指定不同的功能。除了作为数字信号引脚之外,一部分

GPIO 引脚也可以配置为 ADC 模拟引脚。所有 GPIO

都可以在内部被设置为上拉、下拉、高阻,当

GPIO

被配置为输入状态,则可以通过读取寄存器获取该状态值。已经被设置为输入状态的

GPIO

引脚,可以产生出信号边缘触发或者电平状态触发中断。

注意:ESP32-C3 的数字 GPIO 引脚都是双向、非反相、三态的,因而这些引脚也可以被复用为

UART、SPI等其它用途。

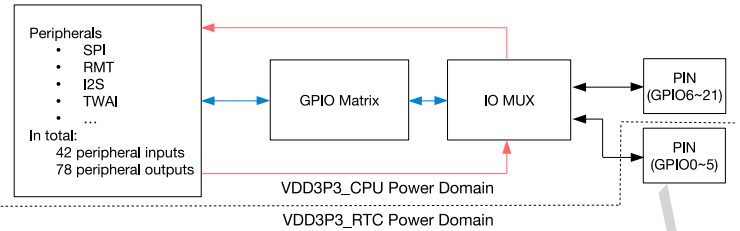

ESP32-C3 的 IO MUX 和 GPIO 交换矩阵用于将信号从外设传输至 GPIO 引脚,两者共同控制着 ESP32-C3 的输入输出:

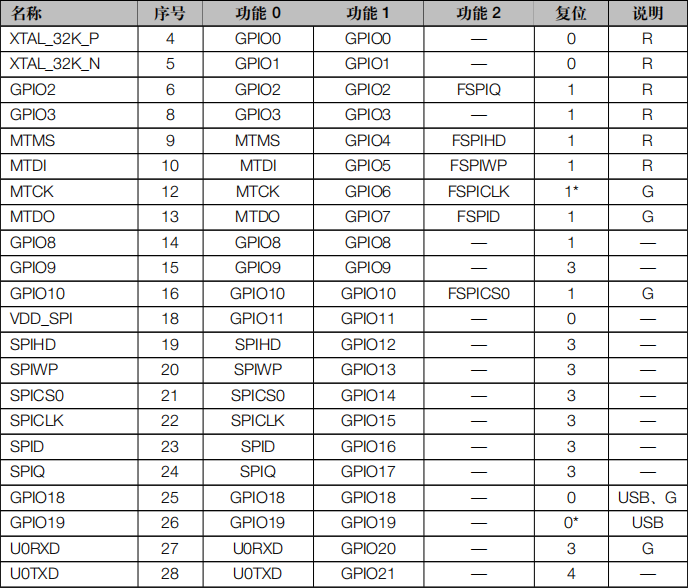

下面的表格展示了所有通过 IO MUX 和 GPIO 交换矩阵 所映射出的引脚功能:

注意:

GPIO12和GPIO13在 Arduino 的 QIO 模式下被复用为 SPI 总线的SPIHD和SPIWP信号线,为了增加可用的 GPIO 数量,UINIO-MCU-ESP32C3 采用了两线制 SPI 的 DIO 模式,使用时需要注意将 Flash 配置为 DIO 模式。除此之外,GPIO11默认为 SPI Flash 的VDD_SPI引脚,需要配置之后才能够复用为 GPIO 使用。

下面展示了上述表格当中,复位一栏各个符号所代表的含义:

| 复位状态序列号 | 默认配置说明 |

|---|---|

| 0 | 输入关闭,高阻 (IE = 0) |

| 1 | 输入使能,高阻 (IE = 1) |

| 2 | 输入使能,下拉电阻使能

(IE = 1,WPD = 1) |

| 3 | 输入使能,上拉电阻使能

(IE = 1,WPU = 1) |

| 4 | 输出使能,上拉电阻使能

(OE = 1, WPU = 1) |

| 0* | 输入关闭,上拉电阻使能

(IE = 0,WPU = 0,USB_WPU = 1) |

| 1* | 当 eFuse 的

EFUSE_DIS_PAD_JTAG 位为 0

时(默认值),引脚复位之后输入使能,上拉电阻使能

(IE = 1,WPU = 1);而当 EFUSE_DIS_PAD_JTAG 被置为 1

时,引脚复位之后输入使能,且处于高阻状态

(IE = 1)。 |

在上面表格当中,说明一栏里符号所代表的含义如下所示:

- R:该引脚具有模拟功能;

- G:该引脚在芯片上电过程当中存在毛刺;

- USB:

GPIO18和GPIO19属于 USB 引脚,其上拉电阻由引脚上拉和 USB 上拉共同控制,当其中任意一个为1时,对应引脚的上拉电阻使能;USB 上拉由USB_SERIAL_JTAG_DP_PULLUP位进行控制;

注意:建议将处于高阻状态的引脚配置为

上拉或者下拉,从而避免不必要的电能消耗。

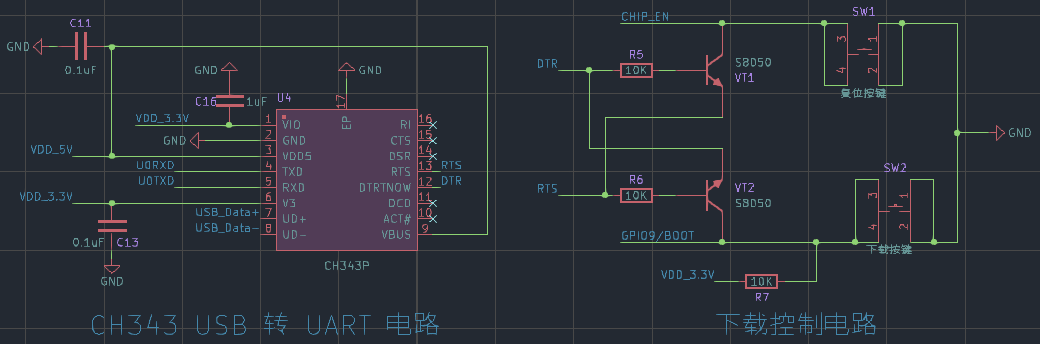

UART0 自动下载

当 ESP32-C3 复位完成之后,就可以通过

GPIO2、GPIO8、GPIO9 三个

Strapping 引脚共同控制 Boot 模式:

- 在 SPI Boot 模式下,ESP32-C3 会通过从 SPI Flash 存储器当中读取程序进行启动,此模式下可以进一步细分为常规 Flash 启动方式(支持安全启动,程序运行在 RAM 中)和直接启动方式(不支持安全启动,程序直接运行在 Flash 中)这两种启动方式;

- 在 Download Boot 模式下,可以通过

UART0或者 USB 接口将代码下载至 Flash,或者将程序加载至 SRAM 并在 SRAM 当中运行(确保.bin文件当中地址为0x42000000的前两个字为0xaedb041d);

UINIO-MCU-ESP32C3 的 GPIO2

在默认情况下,已经在内部被弱上拉为 3.3V

高电平(此处存疑,因为根据官方文档,该引脚实际上为输入高阻状态,并非处于高电平,可能文档撰写过程当中存在着谬误,了解该问题的同学可以联系我);而

GPIO8 通过外接上拉电阻 R4

也被钳制为高电平。此时 ESP32-C3

进入【下载启动模式】的条件就转变为:当

CHIP_EN

引脚上面的信号处于上升沿的时候,Strapping 引脚

GPIO9 必须保持为低电平 0。

通过上面的原理图可以看到,GPIO9/BOOT 和

CHIP_EN 分别连接至 ESP32-C3 的集电极,此时

USB 转串口芯片 DTR 与 DTR 引脚,以及三极管

Q1 与 Q2 和 ESP32-C3

的 CHIP_EN、GPIO9

引脚之间的逻辑关系如下表所示:

| 串口 DTR 和 DTR 状态 | 三极管 Q1 和 Q2 状态 | ESP32-C3 引脚状态 |

|---|---|---|

DTR = 0 并且

RTS = 0 |

Q1 截止,Q2 截止 | CHIP_EN = 1、GPIO9 = 1 |

DTR = 0 并且

RTS = 1 |

Q1 截止,Q2 导通 | CHIP_EN = 1、GPIO9 = 0 |

DTR = 1 并且

RTS = 0 |

Q1 导通,Q2 截止 | CHIP_EN = 0、GPIO9 = 1 |

DTR = 1 并且

RTS = 1 |

Q1 截止,Q2 截止 | CHIP_EN = 1、GPIO9 = 1 |

概而言之,当 USB 转串口芯片的 DTR 和 RTS

同时为 0 或者 1 的时候,三极管

Q1 和 Q2 均处于截止状态,此时

CHIP_EN 和 GPIO9

的状态由内外部的上下拉电阻决定。而当串口芯片的 DTR 和

RTS 不同时为 0 或者 1

时,CHIP_EN 与 RTS 的电平状态,以及

GPIO9 与 DTR 的电平状态完全相同。这就意味着

CHIP_EN 与 IO0 不可能同时为

0,然而进入下载模式需要 CHIP_EN 在从

0 向 1 跳变时,GPIO9

的电平状态持续等于

0。为了满足这个条件,ESP32-C3 的

CHIP_EN 引脚被连接到了一个 RC

充放电电路上面,具体可以参见 UINIO-MCU-ESP32C3

的原理图:

由于电容具有充放电效应,电平状态并不会马上切变为高电平,而是会从

0 缓慢上升至 1,在这个过程当中

GPIO9 维持低电平 0 状态,即当串口芯片的

DTR = 0 并且 RTS = 1 的时候,就可以实现

ESP32-C3 的自动串口下载。

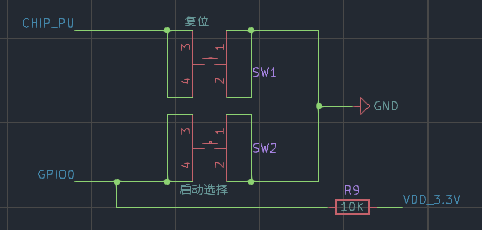

除此之外,UINIO-MCU-ESP32C3 板载的 SW1

和 SW2

两颗按键,分别是实现复位功能的【复位按键】,以及实现下载功能的【下载按键】,具体用途可以参考下面的表格:

| 按键位号 | 功能说明 | 有效值 |

|---|---|---|

SW1 |

按键按下时 ESP32-C3 开始复位 | 低电平 0

有效 |

SW2 |

按键按下时 ESP32-C3 进入下载模式 | 低电平 0

有效 |

UINIO-MCU-ESP32S3 硬件设计

上海乐鑫科技

推出的 ESP32-S3 微控制器基于 Cadence

公司的 Xtensa® Dual-Core 32-bit LX7 架构,拥有

45 个 GPIO 接口,主频高达 240MHz,板载有

384KB 容量的 ROM,以及 512KB 容量的 SRAM 和

16KB 容量的 RTC SRAM,支持的数字外设接口有

4 × SPI、3 × UART、2 × I²C、2 × I²S。而模拟外设接口方面则支持多达

20 通道的 2 × 12 位 SAR 模/数转换器。

ESP32-S3 的核心电路与 ESP32-C3

非常相似,同样仅需要 20

个左右的贴片电阻、电容、电感,以及 1

个无源晶振、1 个 SPI 接口的 Flash 存储芯片和

1 个可选的 PSRAM 存储芯片。下面展示的是

ESP32-S3 的官方参考原理图(基于四线制

3.3V 工作电压的外部 Flash 和

PSRAM 存储器进行设计):

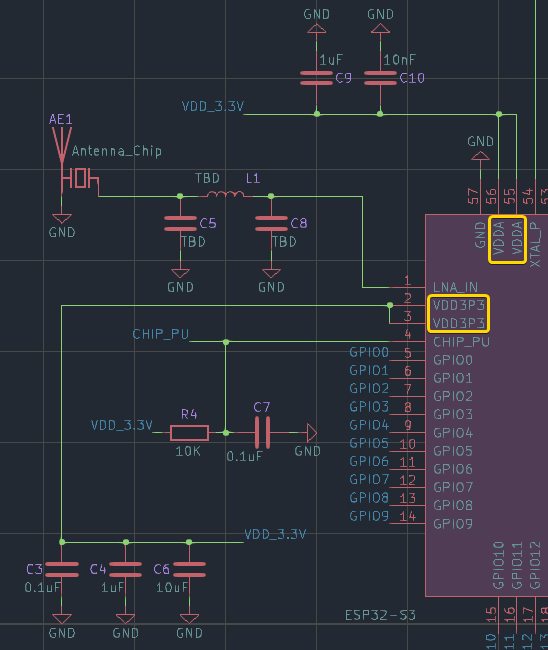

电源

ESP32-S3 的正常工作电压为

3.3V,正常工作所需的最大电流在 500mA

以上,并且电源入口位置建议添加静电释放(ESD,Electro-Static

Discharge)保护元件。整体上看,ESP32-S3 与上面介绍的

ESP32-C3

在电路设计方面的整体区别不大,因而本节内容主要介绍两者在供电电源、系统复位、Flash

与 PSRAM 存储器、Strapping 引脚、USB

自动下载等方面的主要差别。

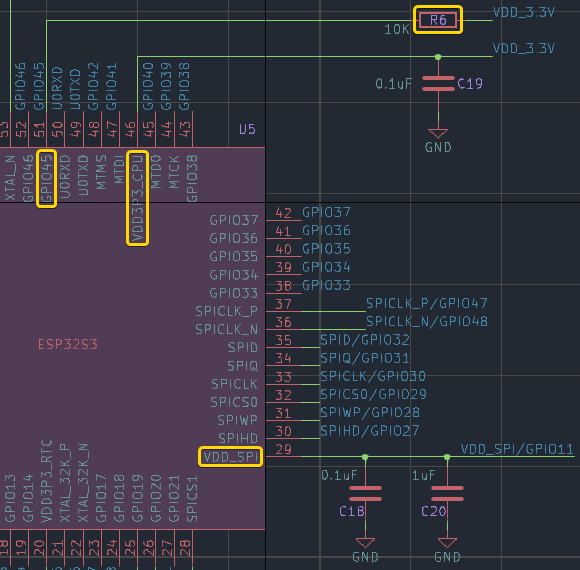

数字电源

ESP32-S3 的第 46 引脚

VDD3P3_CPU 属于微控制器的 VDD

数字电源引脚,其工作电压范围为

3.0V ~ 3.6V,设计时需要在靠近该引脚的位置添加

0.1µF 去耦电容。而第 29 引脚

VDD_SPI 可以被配置为 1.8V 输出(启动时配置

GPIO45 的电平状态为 1)或者

3.3V 输出(启动时配置 GPIO45 的电平状态为

0,即默认状态)给外部电路使用,并且添加 0.1µF

和 1µF 的去耦电容。

- 当

VDD_SPI处于1.8V模式,由 ESP32-S3 内部的 Flash Voltage Regulator 进行供电(最大电流40mA); - 当

VDD_SPI处于3.3V模式,由 VDD3P3_RTC 经过 \(R_{SPI}\) 电阻进行供电,因此VDD_SPI相对于VDD3P3_RTC会存在一定的电压降;

注意:UINIO-MCU-ESP32S3 的

VDD_SPI串联有一枚10KΩ的电阻 \(R_6\),如果采用3.3V工作电压的 Flash 存储芯片,则需要移除 \(R_6\) 电阻,使得 GPIO45 的电平状态默认为0。

模拟电源

ESP32-S3 的第

2、3、55、56

引脚为 VDDA 模拟电源引脚,其工作电压范围为

3.0V ~ 3.6V。类似于 ESP32-C3,为了防止

TX

状态下瞬时电流增大导致的电源轨道塌陷,所以

UINIO-MCU-ESP32S3 在 VDD3P3_CPU

的电源走线上增加了一枚 10µF 电容,并且将其与

1µF、0.1µF 电容并联起来使用。

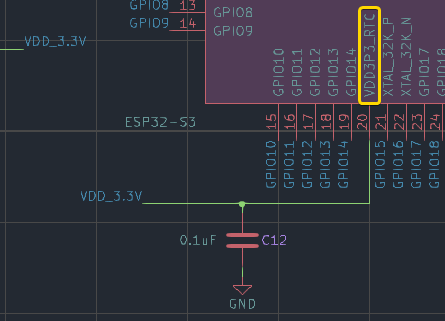

RTC 电源

ESP32-S3 的第 20 引脚

VDD3P3_RTC 属于 RTC

电源引脚,UINIO-MCU-ESP32S3 在该引脚位置添加了一枚

0.1µF 的去耦电容。

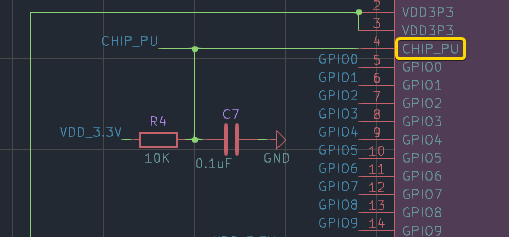

复位

不同于 ESP32-C3 通过 CHIP_EN

引脚进行复位,ESP32-S3 的复位引脚被称为

CHIP_PU。两者除了命名上的不同,其它参数乃至于使用方法基本一致。

Flash 与 PSRAM

ESP32-S3 支持的片外 Flash 和

PSRAM 最大分别可以达到 1GB

存储容量,在元件选型时需要特别注意根据 VDD_SPI

的输出电压,选择相应工作电压的 Flash 和

PSRAM 存储器芯片。

Strapping 引脚

ESP32-S3 拥有

GPIO0、GPIO45、GPIO46、GPIO3

一共四个 Strapping 引脚,也可以像 ESP32-C3

那样通过寄存器 GPIO_STRAPPING 读取这几个引脚的状态值。

在 ESP32-S3 的复位过程当中(上电复位、RTC

看门狗复位、欠压复位、模拟超级看门狗复位、晶振时钟毛刺检测复位),Strapping

引脚会采样当前的电平状态并且存储至锁存器(锁存值为

0 或 1),并一直保持到芯片掉电或者关闭。

- GPIO0、GPIO45、GPIO46 默认连接着内部的弱上下拉电阻,如果这些引脚没有连接外部电路,或者连接的是高阻抗状态,则内部的弱上下拉状态就会决定其输入电平的默认值;

- GPIO3 默认处于浮空状态,其 Strapping 状态可以用于切换内部的 JTAG 信号来源,此时 Strapping 值由外部电路进行控制(这时的外部电路不能处于高阻抗状态);

下面表格列出了用于选择 JTAG 信号来源的

EFUSE_DIS_USB_JTAG、EFUSE_DIS_PAD_JTAG、EFUSE_STRAP_JTAG_SEL

全部寄存器配置组合:

| JTAG 信号源 | EFUSE_STRAP_JTAG_SEL |

EFUSE_DIS_USB_JTAG |

EFUSE_DIS_PAD_JTAG |

|---|---|---|---|

| 见后表 | 1 |

0 |

0 |

| USB Serial/JTAG 控制器 | 0 |

0 |

0 |

| USB Serial/JTAG 控制器 | 无关 | 0 |

1 |

| 片上 JTAG 引脚 | 无关 | 1 |

0 |

| 无 | 无关 | 1 |

1 |

可以通过外部上下拉电阻,或者 GPIO 控制 ESP32-S3 上电复位时的 Strapping 引脚电平。而在复位放开之后,Strapping 引脚就会恢复为普通功能引脚。接下来的表格展示了 ESP32-S3 全部 Strapping 引脚的配置含义。

通过配置 GPIO45 这个 Strapping

引脚的状态,就可以控制 VDD_SPI 的输出电压:

| 引脚 | 默认状态 | 3.3V | 1.8V |

|---|---|---|---|

| GPIO45 | 下拉 | 0 |

1 |

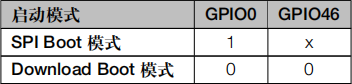

而通过控制 GPIO0 和 GPIO46 这两个 Strapping 引脚的状态,则可以选择 ESP32-S3 的系统启动模式:

| 引脚 | 默认状态 | SPI 启动模式 | 下载启动模式 |

|---|---|---|---|

| GPIO0 | 上拉 | 1 |

0 |

| GPIO46 | 下拉 | 无关 | 0 |

当

EFUSE_DIS_USB_JTAG = 0、EFUSE_DIS_PAD_JTAG = 0、EFUSE_STRAP_JTAG_SEL=1

的时候,则可以通过 GPIO46 选择 JTAG 信号的来源:

| 引脚 | 默认状态 | 引脚状态值为 0 | 引脚状态值为 1 |

|---|---|---|---|

| GPIO46 | 下拉 | JTAG 信号来源于芯片上的 JTAG 引脚 | JTAG 信号来源于 USB Serial/JTAG 控制器 |

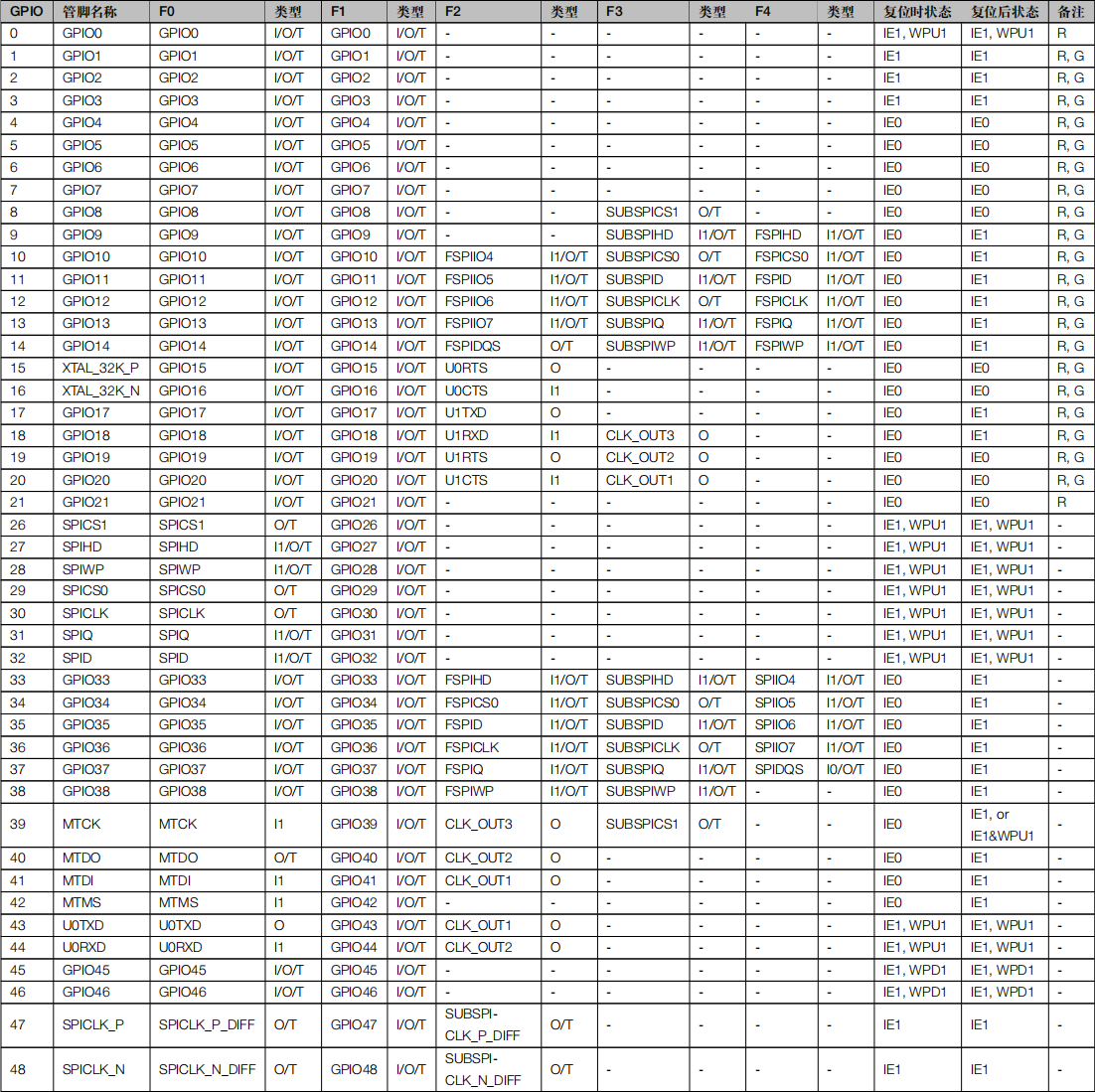

GPIO 引脚

ESP32-S3 一共拥有 45 个 GPIO 数字引脚,它们可以被分配为 \(F_{0 \sim 4}\) 这几种不同类型的功能:

上面表格当中,每一项数字功能 \(F_{0 \sim 4}\) 的含义如下所示:

- O:仅仅只是输出;

- O/T:包含输出与高抗阻的组合;

- I/O/T:包含输入、输出、高抗阻的组合;

- I1:只是输入(如果该引脚分配了

\(F_{0 \sim 4}\) 以外的功能,则 \(F_{0 \sim 4}\) 的输入信号恒为

1); - I1/O/T:该功能信号包含输入、输出、高抗阻的组合(如果该引脚分配了

\(F_{0 \sim 4}\) 以外的功能,则 \(F_{0 \sim 4}\) 的输入信号恒为

1); - I0/O/T:该功能信号包含输入、输出、高抗阻的组合(如果该引脚分配了

\(F_{0 \sim 4}\) 以外的功能,则 \(F_{0 \sim 4}\) 的输入信号恒为

0);

而上述表格当中,引脚复位状态的具体含义如下所示:

- IE0:输入关闭;

- IE1:输入使能;

- IE1, WPD1:输入使能,内部弱下拉电阻使能;

- IE1, WPU1:输入使能,内部弱上拉电阻使能;

- IE1, 或者 IE1&WPU1:当

EFUSE_DIS_PAD_JTAG的eFuse位为1时,芯片复位之后MTCK浮空(IE1),而eFuse位为0时,芯片复位之后MTCK连接至内部的弱上拉电阻(IE1&WPU1)。

上面表格当中,备注一栏里各个符号的功能说明如下所示:

R:该引脚具有 RTC 或模拟功能;G:该引脚在芯片上电过程中存在着毛刺;

注意:

GPIO19 ~ GPIO20的默认驱动电流接近40mA,除此之外其它引脚的默认驱动电流接近20mA。

UART0 自动下载

当 ESP32-S3 复位完成之后,就可以通过

GPIO0、GPIO46 两个 Strapping 引脚共同控制 Boot

模式:

- 在 SPI Boot 模式下,ESP32-S3 会通过从 SPI Flash 存储器当中读取程序进行启动,此模式下可以进一步细分为常规 Flash 启动方式(支持安全启动,程序运行在 RAM 中)和直接启动方式(不支持安全启动,程序直接运行在 Flash 中)这两种启动方式;

- 在 Download Boot 模式下,可以通过

UART0 或者 USB OTG 接口将代码下载至

Flash 存储器,或者将程序加载至 SRAM 并在 SRAM 当中运行(需要确保

.bin文件里地址为0x42000000的前两个字为0xaedb041d);

UINIO-MCU-ESP32S3 的 GPIO46

会在复位之后处于输入和内部弱下拉电阻使能状态(IE1、WPD1),即电平状态被下拉为

0,此时 ESP32-S3

进入【下载启动模式】的条件就变为:当 CHIP_PU

引脚上面的信号处于上升沿的时候,Strapping 引脚 GPIO0

必须保持为低电平 0。

类似于之前介绍的 UINIO-MCU-ESP32C3

自动下载电路,ESP32-S3 的 CHIP_PU

引脚也连接有一个 RC 充放电电路,同样利用了电容的充放电效应,在

CHIP_PU 从 0 向 1

跳变的过程中,将 GPIO0 的电平状态维持为低电平

0。这样当串口芯片的 DTR = 0 并且

RTS = 1 时,就可以实现 ESP32-S3

的自动下载。

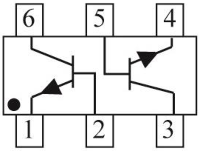

UINIO-MCU-ESP32S3 自动下载电路的不同之处,在于将 UINIO-MCU-ESP32C3 当中由 Q1 和 Q2 两个 NPN 三极管组成的下载逻辑电路,简化为了一颗乐山无线电生产的 LMBT3904DW1T1G 双 NPN 晶体管阵列芯片,该芯片的内部电路与 UINIO-MCU-ESP32C3 的下载逻辑电路接法基本保持一致:

除此之外,UINIO-MCU-ESP32S3 同样板载了

SW1 和 SW2

两颗分别用于实现下载功能和复位功能的按键:

它们的具体用途,与 UINIO-MCU-ESP32C3 上面的两颗按键

SW1 和 SW2 完全保持一致:

| 按键位号 | 功能说明 | 有效值 |

|---|---|---|

SW1 |

按键按下时 ESP32-C3 开始复位 | 低电平 0

有效 |

SW2 |

按键按下时 ESP32-C3 进入下载模式 | 低电平 0

有效 |

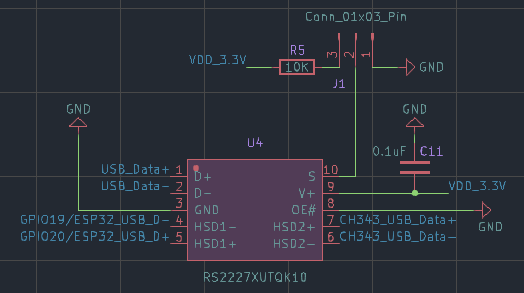

USB OTG 自动下载

ESP32-S3 集成了一颗携带有收发器,并且符合

USB2.0 规范的全速 USB On-The-Go

外设(OTG),其中 GPIO19 和

GPIO20 引脚可以分别用于接入 USB

的差分信号线 D- 和 D+:

利用 ESP32-S3 集成的 USB OTG 外设功能,就可以通过

USB 接口直接进行固件的下载,而无需再借助 CH343P 这类

USB 转串口芯片。UINIO-MCU-ESP32S3 为了同时兼容

UART0 和 USB OTG

两种下载方式,专门加入了一颗由 江苏润石科技

提供的高速低功耗双刀双掷(DPDT,Double Pole Double

Throw)模拟开关 RS2227XUTQK10,其工作电压在

1.8V ~ 5.5V 范围,采用 WQFN-10

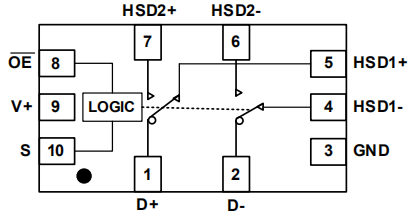

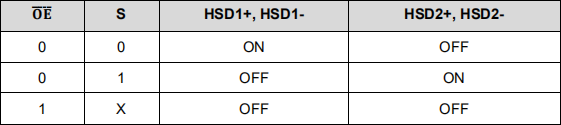

封装,内部原理与引脚连接如下图所示:

上图当中的 D+ 和 D- 是 USB

差分信号输入引脚,而 HSD1+ 和

HSD1-、HSD2+ 和 HSD2- 则分别是

USB 差分信号输出引脚,通过编号为 10 的

S 引脚可以选择当前是使用 HSD1 还是

HSD2 进行 USB

差分信号输出,下面的表格是该芯片各个引脚功能的真值表:

注意:通过原理图当中位号为

J1的跳线座,就可以指定 UINIO-MCU-ESP32S3 当前所使用的下载方式。

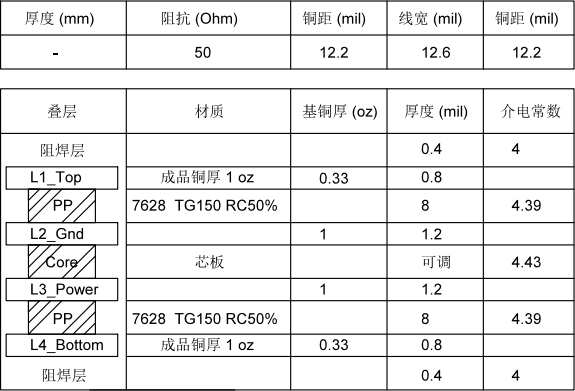

PCB 板图布局注意事项

当采用两层 PCB 进行设计时,可以遵循如下的层功能划分:

- 第 1 层为顶层,主要用于放置元件和走线;

- 第 2 层为底层,尽量不要放置元件,走线越少越好,在确保射频与晶振拥有完整地平面的情况下,可以适度走信号线;

而采用四层 PCB 进行设计时,则可以遵循下面的层功能划分:

- 第 1 层为顶层,用于信号线和放置元件;

- 第 2 层为地层,不走信号线,确保一个完整的地平面;

- 第 3 层为电源层,铺地平面,将电源走在该层;

- 第 4 层为底层,铺地平面,不建议放置元件,在确保射频与晶振拥有完整地平面的情况下,可以适度走信号线;

- 天线:PCB 微带天线尽量靠近 PCB 边缘进行摆放,并且禁止底部覆铜,同时需要注意外壳对于天线射频性能的影响;

- 晶振:让 ESP32 主控芯片与晶振保持一定的距离避免相互干扰,周围不能出现电感之类的磁感应元器件;晶振的信号线最好进行包地处理,并且尽可能的避免走线出现过孔,同时晶振下方禁止通过高频数字信号;

- 射频天线:射频走线需要做

50Ω的单端阻抗控制,参考平面为第二层,射频走线上的 \(\pi\) 型阻抗匹配网络需要呈 Z 字型摆放;射频走线必须保证相邻层拥有完整的地平面,并且走线下方尽可能不要出现任何的走线;射频走线必须远离晶振、DDR、USB 转串口等高频元器件; - Flash 存储器:SPI 总线的时钟与数据走线,最好都进行单独的包地处理;

- USB 转 UART:USB

按照差分信号进行走线,保持平行等长,拥有完整的参考地平面;而

U0TXD和U0RXD走线要尽量缩短,并且最好是进行包地处理;

UINIO-MCU-ESP32 系列核心板电路设计