IEEE1394 FireWire 火线接口物理层硬件设计

IEEE1394 是一种高速实时串行通信总线标准。最早由美国苹果公司推出,被称作火线(FireWire)接口,相关专利主要由美国的苹果(Apple)、德州仪器(TI)和日本的索尼(SONY)、松下(Panasonic)、东芝(Toshiba)、日立(HITACHI)、佳能(Canon),韩国的乐金(LG)以及欧洲的飞利浦(Philips)、意法半导体(ST)等商业公司持有。但是进入到 2011 年之后,苹果公司开始引入更加快速的 Thunderbolt 接口来取代 FireWire 标准,并于 2015 年之后逐渐过度到符合 USB 3.1 规范的 USB Type-C 接口,目前在消费类电子领域已经比较少使用该接口标准。

然而得益于 IEEE1394b 简单的线束结构,该协议的应用也从消费类电子领域,扩展到航空航天领域。美国汽车工程师协会(SAE,Society of Automotive Engineers)基于 IEEE1394b 规范,增加了通信的确定性(包括网络拓扑预分配、强制根节点、带宽预分配、帧开始数据包同步、异步流数据包、静态分配通道号)和可靠性(纵向奇偶校验、健康状态字、心跳字、控制计算机 分支状态字)相关的约束,进一步制定出了适用于航空航天领域的《SAE AS5643B-2016》标准。

IEEE1394 标准演进历史

相比较于同时期的 USB1.1

接口标准,IEEE1394a

标准在数据传输速率上占据着绝对优势,但是当 USB2.0

标准推出之后,IEEE1394a

接口在传输速度上的优势就不再明显;而后续传输速率高达 5Gbps

以上的 USB3.0 接口标准的出现,使得

IEEE1394

规范的后续版本在速度和成本上处于劣势,因而逐渐在消费级市场处于被边缘化的地位:

- IEEE 1394-1995(FireWire

400):采用半双工传输,在不同的传输模式

S100/200/400下面,其理想传输速率分别可以达到100/200/400 Mbit/s。传输线缆最长可以达到 4.5 米,并使用 6 针 阿尔法(Alpha)连接器。 - IEEE 1394a-2000(改进 FireWire 400):澄清和改进了原始规范,增加了异步流、更快的总线重配置、数据包串接、省电暂停模式。最大优点在于其允许总线加速仲裁周期提高效率,并且支持仲裁短总线复位(Arbitrated Short Bus Reset),可以在添加或者移除节点时降低传输速率。同时该标准还吸纳了日本索尼(SONY)公司定义的 i.LINK 四芯连接器(不包含电源连接)。

- IEEE 1394b-2002(FireWire

800):引入了全新的

8b/10b编码方案,允许设备以800 Mbit/s速率全双工运行,并采用了九芯的贝塔(Beta)连接器(无法向下兼容)。 - IEEE 1394c-2006(FireWire

S800T):允许通过以太网 RJ45 连接器提供高达

800 Mbit/s的传输速率。 - IEEE 1394c-2008(FireWire

S1600/S3200):该标准可以让九芯贝塔(Beta)连接器的传输速率达到

1.6/3.2 Gbit/s,但是后续的应用普及非常缓慢。

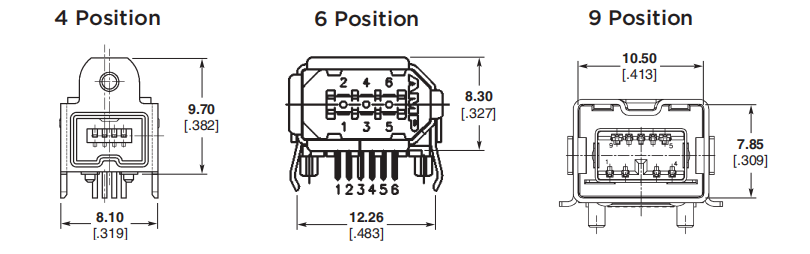

连接器 & 线缆

下图从左至右分别展示了简化掉电源引脚的 4 Pin 引脚的 Mini IEEE1394a 连接器、6 Pin 引脚的标准 IEEE1394a 连接器,以及 9 Pin 引脚的 IEEE1394b 标准连接器。

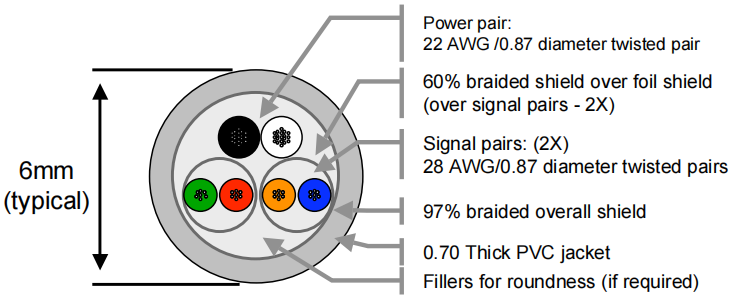

以 IEEE1394a 标准为例,6 Pin 引脚的连接器使用的是 6

芯传输线缆,其外层为屏蔽层,内置有两对双绞线(分别用于传送数据和时钟信号),以及一对电源线(电压范围

8V ~ 40V,额定电流

1.5A),线缆的剖面如下图所示:

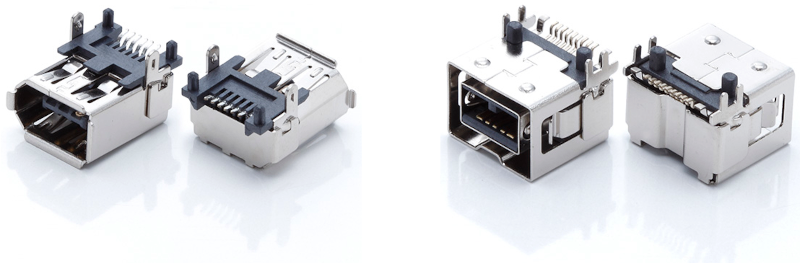

截止到本文撰写时的 2026

年,市面上比较通用,且出货量比较大的是 台湾雅安科技

Accurate 推出的 6Pin 规格

IENF-061N 型(下图左)以及 9Pin 规格

IENF-092N 型(下图右),这两款

IEEE1394 标准连接器:

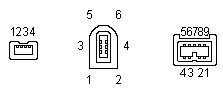

IEEE1394 连接器线序定义

下面的表格,展示了常用的

4Pin、6Pin、9Pin 规格 IEEE1394

连接器的线序与引脚功能定义:

| 4Pin 引脚编号 | 6Pin 引脚编号 | 9Pin 引脚编号 | 引脚名称 | 功能描述 | 线束颜色参考 |

|---|---|---|---|---|---|

| - | 1 |

8 |

Power | 电源正极 | 白色 |

| - | 2 |

6 |

GND | 电源地和屏蔽地 | 黑色 |

1 |

3 |

1 |

TPB- | 双绞线 B 差分信号负 | 橙色 |

2 |

4 |

2 |

TPB+ | 双绞线 B 差分信号正 | 蓝色 |

3 |

5 |

3 |

TPA- | 双绞线 A 差分信号负 | 红色 |

4 |

6 |

4 |

TPA+ | 双绞线 A 差分信号正 | 绿色 |

| - | - | 5 |

屏蔽 A | - | - |

| - | - | 7 |

- | - | - |

| - | - | 9 |

屏蔽 B | - | - |

| 外壳 | 外壳 | 线束屏蔽层 | - | - | - |

注意:上述表格中的引脚编号对应着示意图里的引脚序号。

USB2.0 & IEEE1394 性能比较

| 参数 | 标准 IEEE 1394 | USB 2.0 接口 |

|---|---|---|

| 标准传输速率 | 400 Mbps |

480 Mbps |

| 持续读速度 | 38 MB/s |

33 MB/s |

| 持续写速度 | 35 MB/s |

27 MB/s |

| 连接器循环寿命 | 4 引脚 1000 次,6 引脚

1500 次 |

1500 次 |

| 通信架构 | 点对点结构 | 主从结构 |

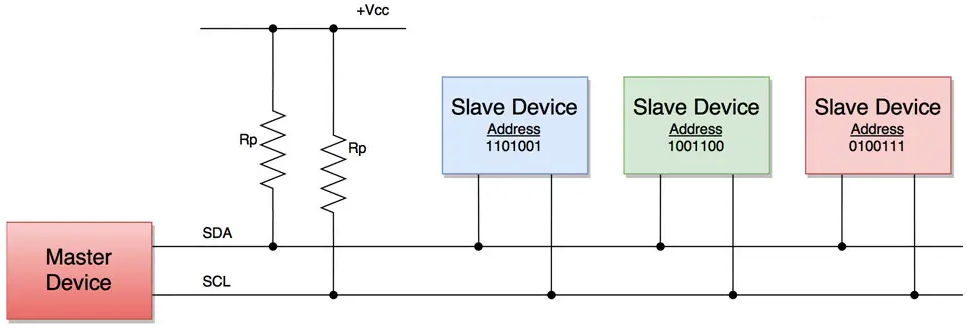

总线基本结构

1394 总线以节点 Node 作为单位来组成通信网络,一个基本的 1394 总线系统由控制计算机节点(CC,Control Computer)、远程节点(RN,Remote Node)、总线监控节点(BM,Bus Monitor)以及 IEEE1394 线缆与连接器共同组成,下图展示了 IEEE1394 总线的基本网络拓扑:

- 控制计算机节点 CC:作为总线控制器,周期性发送帧起始(STOF,Start of Frame)信号,通知总线上所有节点开始发送新的数据帧,并借此实现总线数据同步;

- 远程节点

RN:作为远程终端,根据总线通道预分配,将不同的节点 ID

和通道号进行绑定;RN 节点接收到

STOF帧起始信号之后,就会确认新的数据帧开始,并且按照预先分配的偏移时间,在时间窗口到来时发送数据。 - 总线监控节点

BM:作为叶子节点挂载在总线上,能够监控总线上其它节点发出的

网络管理与普通数据消息,从而实现对于网络数据的分析;

总线上各个节点之间通过 1394 线缆连接,1394 总线线缆是一种物理通信媒介,是网络信号传输的载体。1394 线缆通过连接器与模块进行连接,通过连接器实现不同子系统的中转接口。当节点之间距离过长时,会导致传输信号衰减过大,由此需要通过 1394 总线中继器来完成信号的增强。

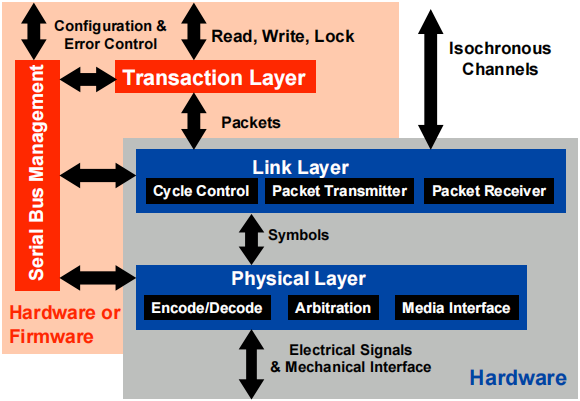

物理层 PHY 芯片

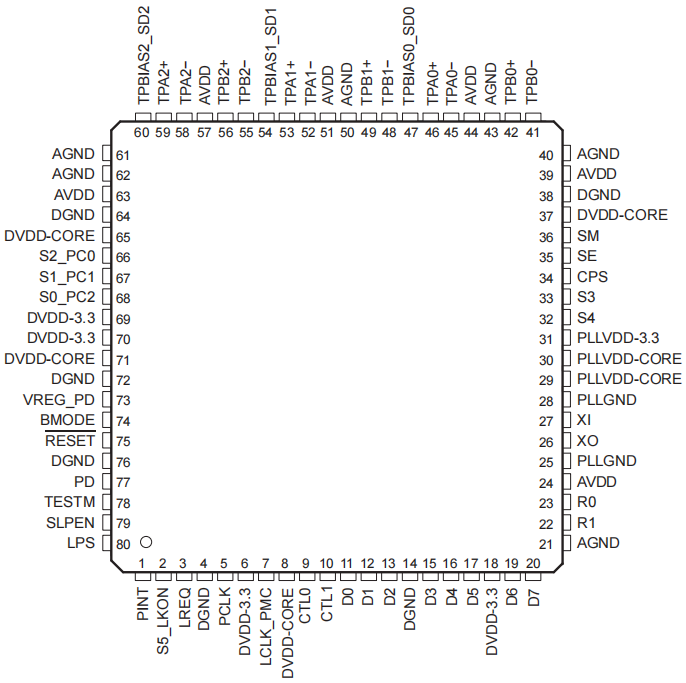

下图展示的是一款同时支持 IEEE 1394-1995、IEEE 1394a-2000、IEEE 1394b-2002 协议标准的 PHY 物理层芯片的引脚定义图:

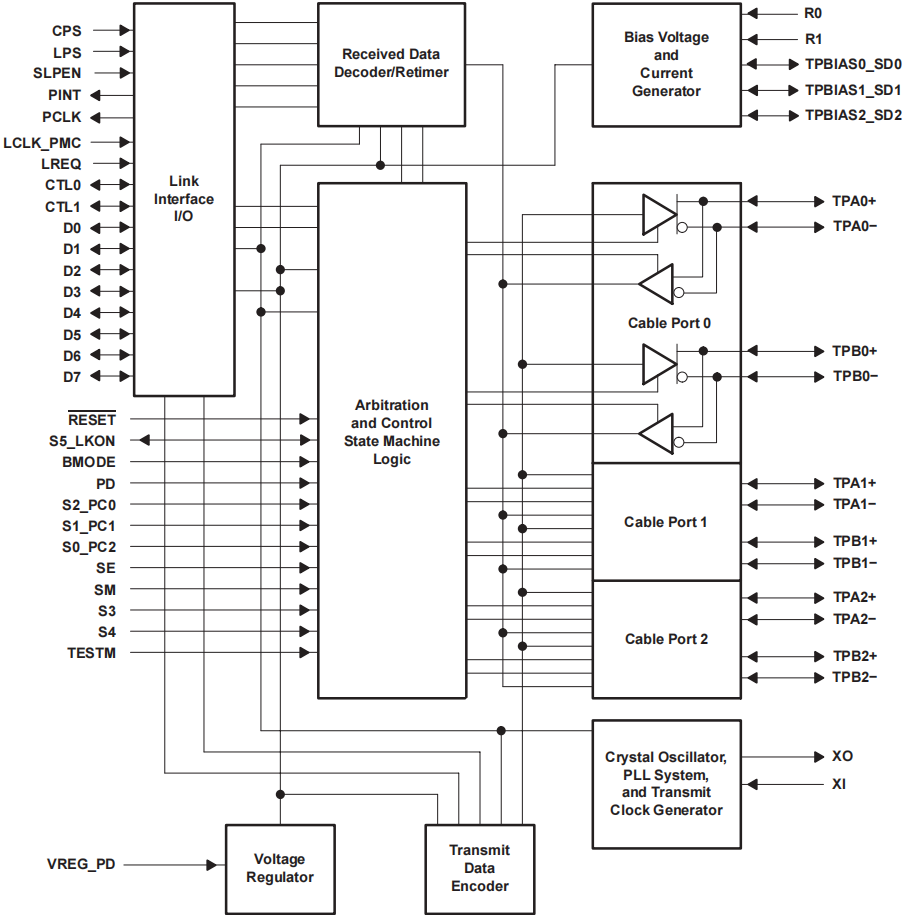

接下来的示意图,则展示了上面这片 PHY 物理层芯片内部的基本功能框图:

物理层(PHY,Physical Layer)芯片通常需要与链接层控制器 (LLC,Link Layer Controller) 搭配起来使用,两者各司其职。下面的表格对上述 PHY 芯片的引脚定义进行了详细的说明:

| 名称 | 类型 | 编号 | I/O | 功能描述 |

|---|---|---|---|---|

| AGND | 电源 | 21/40/43/50/61/62 |

- | 模拟接地引脚。 |

| AVDD | 电源 | 24/39/44/51/57/63 |

- | 模拟电源引脚,建议并联 0.1uF 和 0.001 uF

高频去耦电容,以及 10uF 低频去耦电容。 |

| BMODE | CMOS | 74 |

输入 | Beta 模式输入,用于决定

PHY<->Link 接口的连接协议(高电平为

IEEE1394b-2002,低电平为 IEEE1394a-2000) |

| CPS | CMOS | 34 |

输入 | 线缆电源状态(CPS,Cable power

status)输入引脚,通常使用 400KΩ

电阻连接到线缆上的电源,然后通过内部比较器检测线缆电源是否存在(没有检测到电源,就会向

LLC 生成中断)。 |

| CTL0/1 | CMOS | 9/10 |

输入 | 控制 IO 引脚,用于控制 PHY 与 LLC 之间的双向控制通信。 |

| D0 ~ D7 | CMOS | 11/12/13/15/16/17/19/20 |

输入 | 数据 IO 引脚,用于控制 PHY 与 LLC 之间的双向数据通信。 |

| DGND | 电源 | 4/14/38/64/72/76 |

- | 数字接地引脚。 |

| DVDD-CORE | 电源 | 8/37/65/71 |

- | 数字核心电源,建议并联

0.001 uF、0.1uF、1uF

去耦电容。 |

| DVDD-3.3 | 电源 | 6/18/69/70 |

- | 数字 3.3V 电源,建议并联

0.001 uF、0.1uF、10uF

去耦电容。 |

| LCLK_PMC | CMOS | 7 |

输入 | Link 时钟与复位电源管理控制输入引脚,LINK->PHY 提供

98.304MHz

的时钟信号用于同步数据传输,硬件重置时,该引脚的采样决定了电源管理控制(PMC,Power

Management Control)的模式。 |

| LPS | CMOS | 80 |

输入 | Link 电源状态(LPS,Link Power Status)输入引脚,用于监视 LLC

控制器的活动状态,并且控制 PHY<->Link

接口的状态。 |

| LREQ | CMOS | 3 |

输入 | LLC 请求(Request)输入引脚,链接层控制器 LLC 使用该引脚向 PHY 发起服务请求。 |

| PCLK | CMOS | 5 |

输出 | PHY 时钟输出引脚,当 PHY->LINK 处于

IEEE1394b-2002 模式时,提供 98.304MHz

的时钟信号用于同步数据传输。如果处于 IEEE1394a-2000

模式,则只提供 49.152MHz 的时钟信号。 |

| PD | CMOS | 77 |

输入 | 下电输入,高电平时关闭全部内部电路,同时激活 RESET 引脚的内部下拉,从而强制重置内部控制逻辑。 |

| PINT | CMOS | 1 |

输出 | PHY 中断,当 PHY<->Link 接口处于 1394b

工作模式时,用于输出串行传输状态给 Link 层控制器。 |

| PLLGND | 电源 | 25/28 |

- | PLL 锁相环电路接地。 |

| PLLVDD-CORE | 电源 | 29/30 |

- | PLL 锁相环核心电路电源,建议并联

0.001 uF、0.1uF、1uF

去耦电容,该引脚必须与 DVDD-CORE 分开独立供电。 |

| PLLVDD-3.3 | 电源 | 31 |

- | PLL 锁相环的 3.3V 电源引脚,建议并联

0.001 uF、0.1uF、10uF

去耦电容。 |

| RESET | CMOS | 75 |

输入 | 重置输入引脚,低电平时重置内部逻辑,其内部包含有一个连接到 VDD 的上电阻,所以执行上拉时外部只需要一个延迟电容 |

| R0/R1 | 偏置 | 22/23 |

- | 电流配置电阻引脚,用于配置内部操作电流以及电缆驱动器的输出电流,为了满足

IEEE1394-1995 的输出电压要求,建议使用一枚精度为 ±1% 的

6.34 kΩ 电阻器。 |

| SE | CMOS | 35 |

输入 | 测试控制输入引脚,用于生产制造测试,常规使用时必须通过

1kΩ 电阻下拉至 GND 或者直接连接到 GND。 |

| SLPEN | CMOS | 79 |

输入 | 自动休眠模式使能引脚,用于开启自动休眠模式,低电平时保持常规的 1394b 功能。 |

| SM | CMOS | 36 |

输入 | 测试控制输入引脚,用于生产制造测试,常规使用时必须通过

1kΩ 电阻下拉至 GND 或者直接连接到 GND。 |

| S2_PC0/S1_PC1/S0_PC2 | CMOS | 66/67/68 |

输入 | 端口休眠和模式选择引脚 0、1、2(通过 1kΩ

上下拉电阻来实现)。 |

| S3/S4 | CMOS | 33/32 |

输入 | 端口休眠和模式选择引脚 3 和 4(通过 1kΩ

上下拉电阻来实现)。 |

| S5_LKON | CMOS | 2 |

输入/输出 | 端口休眠和模式选择引脚 5;除此之外,该引脚还可以作为

Link-on 输出,通过 1kΩ 电阻连接到 LLC 控制器的

Link-on 输入引脚。 |

| TESTM | CMOS | 78 |

输入 | 测试控制输入引脚,用于生产制造测试,常规使用时必须通过连接到

VDD 的 1kΩ 电阻进行上拉。 |

| TPA0−/+、TPB0−/+ | 线缆 | 45/46/41/42 |

输入/输出 | 差分双绞线 0 端口。 |

| TPA1−/+、TPB1−/+ | 线缆 | 52/53/48/49 |

输入/输出 | 差分双绞线 1 端口。 |

| TPA2−/+、TPB2−/+ | 线缆 | 58/59/55/56 |

输入/输出 | 差分双绞线 2 端口。 |

| TPBIAS0/1/2_SD0/1/2 | 线缆接入 | 47/54/60 |

输入 | 双绞线偏置输出和信号检测输入,用于为双绞线驱动接收器提供

1.86V 偏置电压,并且表明在 IEEE1394a-2000

模式下存在活动的线缆连接,使用时该引脚必须使用 1uF 电容与

GND 解耦,未使用可以不连接。如果 PHY 芯片被配置为 Beta

模式,则该端口转变为输入引脚,此时必须在可用信号到来之时被上拉为高电平。 |

| VREG_PD | CMOS | 73 |

输入 | 稳压器电源下拉输入,高电平时关闭芯片内部的 3.3V 转

1.8V 稳压器,对于仅有 3.3V

的操作,则该引脚必须连接到 GND。 |

| XI/XO | 晶振 | 26/27 |

输入/输出 | 晶体振荡器输入,连接到 49.152 MHz

晶体振荡器,XI 是一个 1.8V CMOS 输入。 |

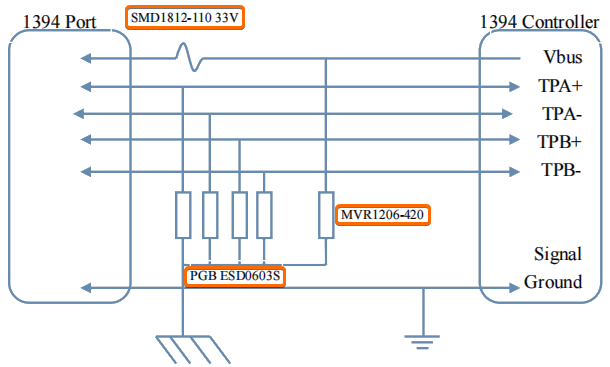

IEEE1394 接口保护电路

IEEE1394 使用介于 1.2V ~ 2.0V

范围的差分信号传输数据,最大数据传输速率为 IEEE1394a 的

400 Mbps 到 IEEE1394b 的

1600 Mbps,因此在该速率范围之内,TPA+/-、TPB+/-

两组四条信号线上,需要尽可能的选择寄生电容较低的静电释放(ESD,Electro

Static Discharge)元器件。除此之外,也需要防止 30V 直流电源

ESD 以及过电流危害。

SMD1812-110 33V自恢复保险丝:用于总线电源的过电流保护。MVR1206-420防浪涌压敏电阻:用于连接器总线电源的 ESD 静电释放。PGB-ESD0603S双向瞬态电压抑制二极管:用于连接器信号线路的 ESD 静电释放。

注意:总而言之,IEEE1394 连接器的接口电路设计,遵循着串联器件用于电流防护,并联器件用于电压防护的基本设计原则。

IEEE1394 FireWire 火线接口物理层硬件设计